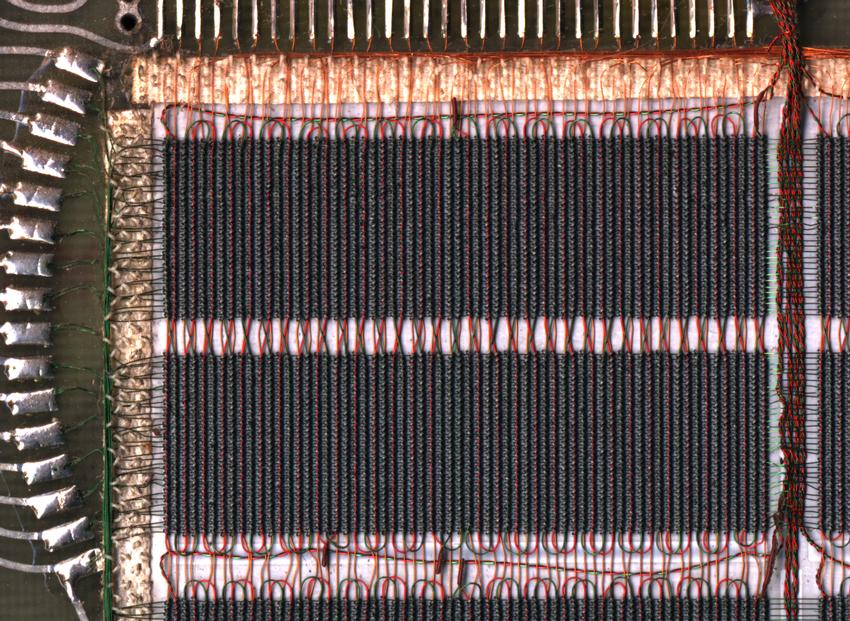

This is the upper left corner from the G619A (119K) core memory board. When viewed on large each pixel is 1/1200 of an inch. Each dense strip consists of a 64 by 32 (2048) array of cores and the two strips in the picture store one bit by 4096 locations. These two strips are equivalent to a single chip in the later semiconductor memory board. To reduce noise the 4096x1 core plane was split in two pieces with the sense/inhibit wire crossing between the core columns. This acts like a twisted pair wire so the read noise on the sense line becomes common mode and is rejected by the differential sense amplifier.

Each core takes about .0148x.025 inches with the ferrite toroid .022x.007. The wires appear to be about .003 inch diameter, 40 gauge. Three of these wires run through each toroid. The twisted bundles of wires are the sense/inhibit lines which run through each of the 4096 cores. You can see it looping between the columns of cores. The blobs on the wires at the edge of each mat where the sense line is looping through the cores are splices. Threading one wire without breaks may have been difficult. Running top to bottom is the Y lines and side to side are the X lines.

Back to Previous page All of PDP-8/E Board pictures

Feel free to contact me, David Gesswein djg@pdp8online.com with any questions, comments on the web site, or if you have related equipment, documentation, software etc. you are willing to part with. I am interested in anything PDP-8 related, computers, peripherals used with them, DEC or third party, or documentation.

PDP-8 Home Page PDP-8 Site Map PDP-8 Site Search